REVIEW ARTICLE | NOVEMBER 25 2024

# (Ultra)wide bandgap semiconductor heterostructures for electronics cooling $\boldsymbol{\boldsymbol{\oslash}}$

Zhe Cheng **⊠** ⓑ ; Zifeng Huang ⓑ ; Jinchi Sun ⓑ ; Jia Wang ⓑ ; Tianli Feng ⓑ ; Kazuki Ohnishi ⓑ ; Jianbo Liang ⓑ ; Hiroshi Amano ⓑ ; Ru Huang

() Check for updates

Appl. Phys. Rev. 11, 041324 (2024) https://doi.org/10.1063/5.0185305

### Articles You May Be Interested In

Transforming underground to surface mining operation – A geotechnical perspective from case study

AIP Conference Proceedings (November 2021)

Monthly prediction of rainfall in nickel mine area with artificial neural network

AIP Conference Proceedings (November 2021)

Estimation of Karts groundwater based on geophysical methods in the Monggol Village, Saptosari District, Gunungkidul Regency

AIP Conference Proceedings (November 2021)

Special Topics Open for Submissions

Learn More

## (Ultra)wide bandgap semiconductor heterostructures for electronics cooling

Cite as: Appl. Phys. Rev. **11**, 041324 (2024); doi: 10.1063/5.0185305 Submitted: 20 November 2023 · Accepted: 29 October 2024 · Published Online: 25 November 2024

Zhe Cheng,<sup>1,2,a)</sup> D Zifeng Huang,<sup>1,3</sup> D Jinchi Sun,<sup>4</sup> D Jia Wang,<sup>5</sup> D Tianli Feng,<sup>6</sup> Kazuki Ohnishi,<sup>5</sup> Jianbo Liang,<sup>7</sup> Hiroshi Amano,<sup>5</sup> and Ru Huang<sup>1,2</sup>

#### AFFILIATIONS

<sup>1</sup>School of Integrated Circuits and Beijing Advanced Innovation Center for Integrated Circuits, Peking University, Beijing 100871, China

<sup>2</sup>Frontiers Science Center for Nano-optoelectronics, Peking University, Beijing 100871, China

$^{

m 3}$ School of Energy and Power Engineering, Huazhong University of Science and Technology, Wuhan 430074, China

<sup>4</sup>Department of Materials Science and Engineering and Materials Research Laboratory,

University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA

<sup>5</sup>Center for Integrated Research of Future Electronics, Institute for Materials and Systems for Sustainability,

Nagoya University, Furo-cho, Chikusa-ku, Nagoya 464-8601, Japan

<sup>6</sup>Department of Mechanical Engineering, University of Utah, Salt Lake City, Utah 84112, USA

<sup>7</sup>Department of Physics and Electronics, Osaka Metropolitan University, Gakuen-cho, Naka-ku, Sakai 599-8531, Japan

<sup>a)</sup>Author to whom correspondence should be addressed: zhe.cheng@pku.edu.cn

#### ABSTRACT

The evolution of power and radiofrequency electronics enters a new era with (ultra)wide bandgap semiconductors such as GaN, SiC, and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, driving significant advancements across various technologies. The elevated breakdown voltage and minimal on-resistance result in size-compact and energy-efficient devices. However, effective thermal management poses a critical challenge, particularly when pushing devices to operate at their electronic limits for maximum output power. To address these thermal hurdles, comprehensive studies into thermal conduction within semiconductor heterostructures are essential. This review offers a comprehensive overview of recent progress in (ultra) wide bandgap semiconductor heterostructures dedicated to electronics cooling and are structured into four sections. Part 1 summarizes the material growth and thermal properties of (ultra)wide bandgap semiconductor heterostructures. Part 2 discusses heterogeneous integration techniques and thermal boundary conductance (TBC) of the bonded interfaces. Part 3 focuses on the research of TBC, including the progress in thermal characterization, experimental and theoretical enhancement, and the fundamental understanding of TBC. Parts 4 shifts the focus to electronic devices, presenting research on the cooling effects of these heterostructures through simulations and experiments. Finally, this review also identifies objectives, challenges, and potential avenues for future research. It aims to drive progress in electronics cooling through novel materials development, innovative integration techniques, new device designs, and advanced thermal characterization. Addressing these challenges and fostering continued progress hold the promise of realizing high-performance, high output power, and highly reliable electronics operating at the electronic limits.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0185305

#### TABLE OF CONTENTS

| I. INTRODUCTION                                   | 2 |

|---------------------------------------------------|---|

| II. MATERIALS GROWTH: HIGH QUALITY                |   |

| ACHIEVING HIGH THERMAL CONDUCTIVITY               | 4 |

| A. GaN growth                                     | 4 |

| B. $\beta$ -Ga <sub>2</sub> O <sub>3</sub> growth | 5 |

| C. AlN growth                                     | 5 |

| D. Digital alloys and superlattices     | 7  |

|-----------------------------------------|----|

| E. SiC growth                           | 8  |

| III. HETEROGENEOUS INTEGRATION: BONDING |    |

| WITH HIGH THERMAL CONDUCTIVITY          |    |

| MATERIALS                               | 11 |

| A. Surface-activated bonding            | 12 |

| B. Smart-cut technique                  | 14 |

|                                         |    |

pubs.aip.org/aip/are

| C. Hydrophilic bonding                           | 16 |

|--------------------------------------------------|----|

| D. Plasma bonding                                | 17 |

| E. Other bonding methods                         | 19 |

| F. Summarization of TBC values                   | 20 |

| IV. CHARACTERIZATION, ENHANCEMENT, AND           |    |

| UNDERSTANDING OF TBC                             | 20 |

| A. Thermal characterization of TBC               | 20 |

| 1. Pump-probe techniques                         | 21 |

| 2. 3ω method                                     | 27 |

| 3. Comparison                                    | 27 |

| 4. TBC mapping                                   | 28 |

| B. TBC enhancement                               | 29 |

| 1. Contact area enlargement                      | 29 |

| 2. Interfacial engineering                       | 30 |

| 3. Phonon bridging                               | 31 |

| 4. Other mechanisms                              | 32 |

| C. Fundamental understanding of TBC: Interfacial |    |

| phonon mode                                      | 33 |

| V. DEVICE-LEVEL SIMULATIONS AND                  |    |

| DEMONSTRATIONS                                   | 35 |

| A. Thermal simulations of devices                | 35 |

| B. Experimental demonstrations of device cooling | 38 |

| VI. CHALLENGES AND PERSPECTIVES                  | 40 |

|                                                  |    |

#### I. INTRODUCTION

Compared to Si, (ultra)wide bandgap semiconductors, such as GaN, SiC, and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, exhibit higher breakdown voltage and lower specific on-resistance, resulting in the creation of more compact and efficient devices.<sup>1</sup> For instance, to block the same voltage, GaN and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> require only 9% and 4% of Si material, respectively.<sup>1,2</sup> The Baliga figure of merits (BFOM) of GaN and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, which measures the minimized resistive losses, are 870 and 2870 times of Si, respectively.<sup>1,2</sup>

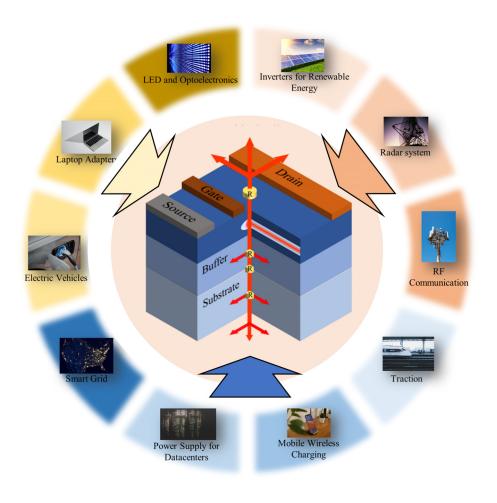

These semiconductors hold immense promise in power electronics and radiofrequency (RF) electronics, ushering in revolutionary applications such as radar systems, satellite communication, 5G stations, renewable energy, electric vehicles, energy infrastructures, and consumer electronics.<sup>1,3</sup> However, the Joule heating in these devices generates localized hot spots, elevating device temperature and subsequently compromising performance and reliability. Consequently, thermal management poses significant challenges in the electrothermal co-design of (ultra)wide bandgap electronics. Furthermore, as the devices become increasingly compact, highly integrated, and highperformance, the challenges of heat dissipation become increasingly serious.

Addressing the heat spreading of localized hotspots within electronic devices necessitates a keen focus on the thermal resistances of semiconductor heterostructures, comprising thin films and interfaces. The quality of grown crystals plays a pivotal role in determining thermal conductivity and in turn, impacts the heat dissipation of electronics. Table I provides a summary of the bandgap and intrinsic thermal conductivity of bulk (ultra)wide bandgap semiconductors at room temperature, with Si included for comparison. The intrinsic thermal conductivity serves as the upper limit of the semiconductor, while the thermal conductivities of corresponding thin films are all reduced due to boundary and defect scatterings of phonons.

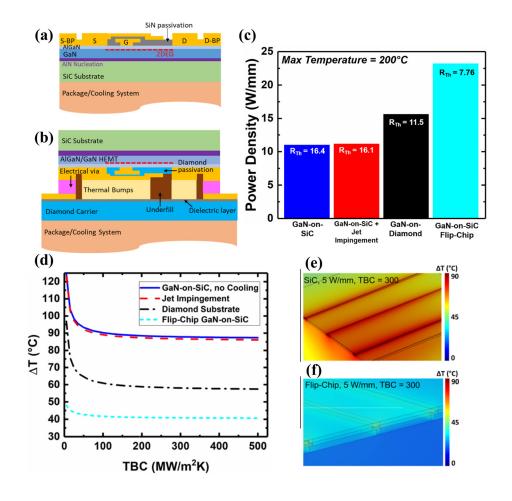

After several decades of development, GaN electronics have carved out a distinctive niche in high-power and high-frequency applications. However, thermal limitations have emerged as a major impediment in realizing the maximum output power from GaN transistors operating near the electronic limit of the material. The hot spots in AlGaN/GaN high-electron mobility transistors (HEMTs) possess extremely small sizes (tens of nanometers) and can exhibit extremely high heat flux (even one order of magnitude higher than that of the Sun's surface), underscoring the critical role of heat spreading in thermal design to mitigate peak temperatures. Moreover, the median lifetime of GaN devices declines by half with every 10 °C increase in channel temperature.<sup>18</sup> Consequently, today's GaN electronics are constrained by thermal considerations, prompting ongoing research efforts to overcome these limitations.<sup>18</sup> The thermal properties within the semiconductor heterostructures are pivotal for thermal management, emphasizing the desirability of high thermal conductivity films and interfaces with elevated thermal boundary conductance (TBC).

Another wide bandgap semiconductor, SiC, exhibits significant potential in high-power electronic devices and has been widely used in electric vehicles.<sup>19</sup> Distinctive thermal properties have been observed in both 4H-SiC and 6H-SiC, which demonstrate thermal conductivities in the range of 300–400 W m<sup>-1</sup> K<sup>-1</sup> as shown in Table I. Recent research has also unveiled a record-high thermal conductivity for wafer-scale high-quality 3C-SiC,<sup>7</sup> which holds the highest electron mobility among all SiC polytypes, suggesting further opportunities for

| Material Band gap/eV                    |         | Thermal conductivity (W $m^{-1} K^{-1}$ ) | Heat capacity (MJ $m^{-3} K^{-1}$ ) | Туре      |  |

|-----------------------------------------|---------|-------------------------------------------|-------------------------------------|-----------|--|

| GaN                                     | 3.4     | 220                                       | 2.63                                |           |  |

| 4H-SiC                                  | 3.3     | 345(out plane), 415(in plane)             | 2.12                                | Wide      |  |

| 6H-SiC                                  | 3.0     | 320(out plane), 390(in plane)             | 2.17                                | Bandgap   |  |

| 3C-SiC                                  | 2.3     | 500                                       | 2.14                                |           |  |

| $\beta$ -Ga <sub>2</sub> O <sub>3</sub> | 4.8     | 27([010]), 11([100])                      | 2.82                                | Ultrawide |  |

| Diamond                                 | 5.5     | 2200                                      | 1.75                                |           |  |

| AlN                                     | 6.2     | 321                                       | 2.44                                | Bandgap   |  |

| $Al_xGa_{(1-x)}N$                       | 3.4-6.2 | 25-115                                    |                                     | 01        |  |

| Si                                      | 1.1     | 142                                       | 1.63                                |           |  |

TABLE I. Summary of bandgap, thermal conductivity, and heat capacity of (ultra)wide bandgap semiconductors at room temperature.<sup>4–17</sup> Si is also added for comparison.

the application of high-performance power devices based on 3C-SiC even though it has relatively small bandgap.

Recently, the ultrawide bandgap semiconductor  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has garnered significant attention due to advances in growth techniques that make large-scale wafer production from melt-grown crystals potentially affordable.<sup>2,3,20</sup>  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> even exhibits a higher BFOM than GaN, with corresponding device demonstrations showing excellent performance.<sup>3,21</sup> However, the intrinsic thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is highly anisotropic and at least one order of magnitude lower than that of the other (ultra)wide bandgap semiconductors.<sup>8,15,22</sup> Moreover, the thermal conductivity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nanostructures is further reduced significantly due to size effects.<sup>22–24</sup> As such, overheating problems in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> electronics represent one of the two main challenges for real-world applications, the other being *p*-type doping.<sup>3</sup> Heterogeneous integration of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> electronics with other high thermal conductivity materials is a possible way to cool these electronics.

Except for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, AlN, which has an ultrawide bandgap, has found extensive use in the field of optoelectronic devices, including deep ultraviolet (DUV) LEDs.<sup>26,27</sup> However, these devices grapple with the issue of overheating, as a substantial portion of the energy is converted into heat.<sup>26</sup> With recent advances to the *p*-doping problem,<sup>27</sup> it is anticipated that there will be an upsurge in AlN electronic and optoelectronic applications, underscoring the significance of enhancing the thermal performance of AlN devices.

This review provides a comprehensive overview of recent advances in the field of (ultra)wide bandgap semiconductor heterostructures for applications of thermal management of electronics. Specifically, it encompasses recent developments in four key areas: (1) Materials growth involving the production of high-quality (ultra)wide bandgap semiconductor crystals and heterostructures with enhanced thermal conductivity; (2) heterogeneous integration strategies for (ultra)wide bandgap semiconductors aimed at electronics cooling; (3) advanced thermal metrology techniques for characterizing the TBC of (ultra) wide bandgap semiconductor heterostructures, experimental and theoretical techniques for enhancing TBC of interfaces as well as the fundamental understanding of TBC, which highlights the recent discovery of localized phonon modes at interfaces; and (4) simulation studies investigating temperature distribution in devices and assessing the efficacy of various cooling methods and evaluation of the practical impact of heterostructures on device cooling and temperature measurement techniques; Fig. 1 shows the motivation and focus of this review. By scrutinizing the state-of-the-art experiment and theory, the aim is to identify key challenges that exist in the cooling of (ultra)wide bandgap electronics and propose potential future research directions to overcome these challenges. This article aims to provide valuable insights

FIG. 1. Motivation and focus of this review.

for researchers and engineers in the field of (ultra)wide bandgap semiconductors.

### II. MATERIALS GROWTH: HIGH QUALITY ACHIEVING HIGH THERMAL CONDUCTIVITY

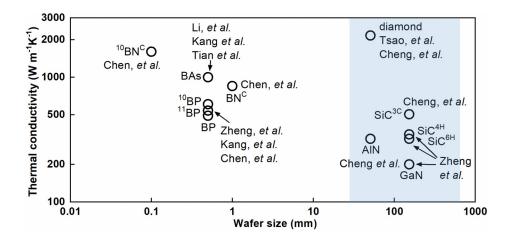

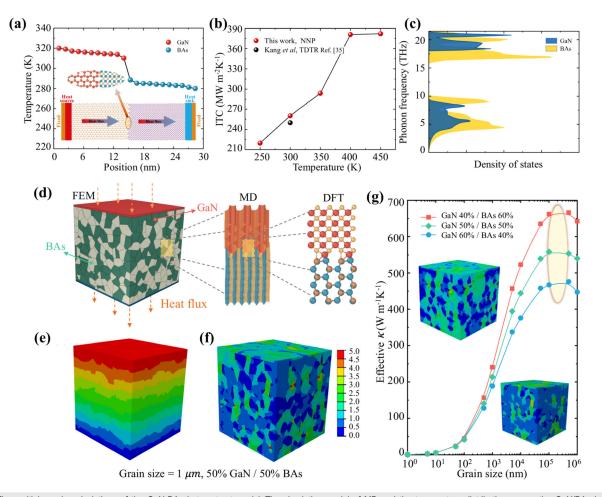

The growth of high-quality and pure materials is essential for achieving high thermal conductivity. Figure 2 provides a summary of the state-of-the-art measured thermal conductivity and wafer size of high thermal conductivity materials.<sup>7</sup> Currently, (ultra)wide bandgap semiconductor materials, including GaN, SiC, diamond, and AlN, can be grown at large wafer size with high thermal conductivity. Although some boron compounds have high thermal conductivity, their mm-scale or smaller crystal size hinders them from being scaled up for massive production and widespread adoption.

The measured thermal conductivity of most (ultra)wide bandgap semiconductors, such as diamond, GaN, 4H-SiC, and 6H-SiC, has reached the intrinsic high values predicted by density functional theory (DFT). This achievement can be attributed to the availability of large wafers with exceptional crystal quality and purity, which eliminate phonon-boundary and phonon-defect scatterings.<sup>16,7</sup> Notably, the measured thermal conductivity of AlN and 3C-SiC has traditionally fallen below the theoretically predicted values. Recent collaborative efforts among researchers in thermal science and material growth, pushing the boundaries of crystal quality and purity, have experimentally observed the intrinsic high thermal conductivity of AlN and 3C-SiC wafers.<sup>7,10</sup>

#### A. GaN growth

Recently, high-quality GaN layers have been laterally overgrown on the mask-patterned sapphire and Si substrates using halide vapor phase epitaxy (HVPE), resulting in a significantly reduced amount of dislocations. The high quality of GaN crystal even grown on foreign substrates has enabled a record-high critical electric field, which approaches the theoretical limit of GaN.<sup>38</sup> Additionally, HVPE has successfully produced high-purity *n*-GaN layers with the highest reported electron mobility at room temperature.<sup>39</sup> In addition, by utilizing MgO as Mg doping source, *p*-type GaN was also fabricated successfully by applying HVPE,<sup>40,41</sup> which also lead to the first demonstration of p-n junction GaN.<sup>42</sup> While no experimental measurements have been reported yet, it is anticipated that high-purity GaN crystals will exhibit high thermal conductivity.

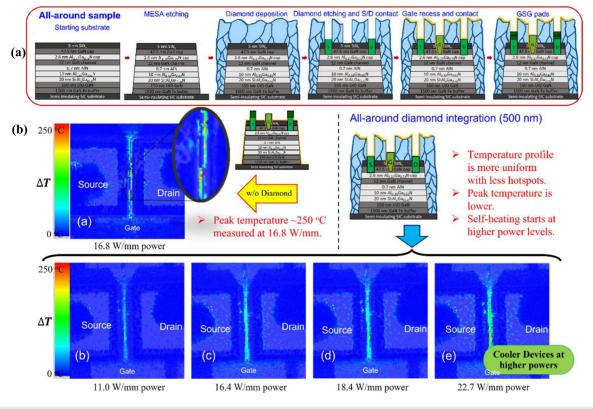

For efficient near-junction heat spreading of GaN electronics, it is preferred to use diamond as the substrate since single-crystal diamond has the highest thermal conductivity among natural materials. However, mismatches in lattices and thermal expansion coefficients between GaN and diamond pose challenges for direct high-quality epitaxial growth of GaN on diamond or vice versa. Polycrystalline diamond, grown on GaN crystals with nanoscale diamond seeds and SiN<sub>x</sub> or AlN dielectric protective layers at the interfacial regions, exhibits orders of magnitude lower thermal conductivity compared to singlecrystal diamond. Moreover, the protective layers introduce additional thermal resistance, limiting the cooling performance of GaN-ondiamond devices.

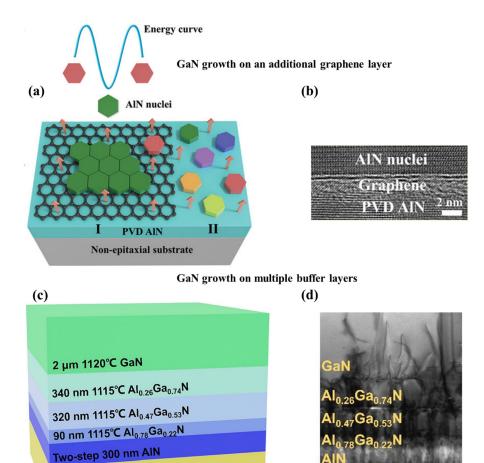

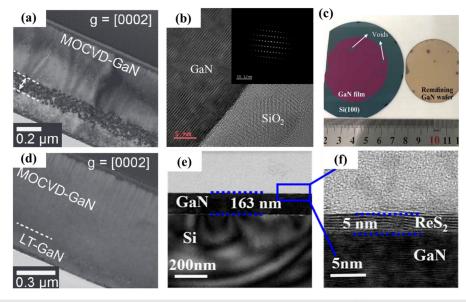

Epitaxial growth of GaN on single-crystal diamond has shown some progress, as depicted in Fig. 3. By incorporating physical vapor deposited (PVD) AlN and graphene on a diamond substrate, a second layer of AlN is grown on top as a transition layer. Subsequent growth of GaN on the AlN transition layer leads to the formation of a uniformly distributed single-crystal continuous film, as shown in Figs. 3(a) and 3(b).<sup>39</sup> However, the additional PVD layer, graphene layer, and corresponding interfaces create significant thermal resistance between the high-quality GaN region and the single-crystal diamond substrate. Furthermore, the GaN layer may exfoliate from the diamond substrate due to the van der Waals interfaces of graphene, posing challenges for device fabrication.

An alternative technique to grow GaN on a single-crystal diamond without graphene involves the growth of multiple AlN and AlGaN transition layers to alleviate stress and lattice mismatch, as illustrated in Figs. 3(c) and 3(d).<sup>43</sup> The orientation of the used diamond substrate is (111). However, obtaining large-area single diamonds with (111) orientation poses a significant challenge. Moreover, AlGaN exhibits low thermal conductivity due to alloy scatterings of phonons. The transition layers and interfaces also create large thermal resistances between GaN and diamond. Unfortunately, the thermal properties of structures grown using these two techniques remain unmeasured, emphasizing the necessity for further studies in both thermal characterizations and the fabrication of practical electronic devices based on these epitaxial layers.

**FIG. 2.** State-of-the-art thermal conductivity values and wafer sizes of high thermal conductivity semiconductors.<sup>1,6,7,10,28–37</sup> Reprinted with permission from Cheng *et al.*, Nat. Commun. **13**, 7201 (2022). Copyright 2022 Springer Nature.<sup>7</sup>

**FIG. 3.** Methods for GaN growth on diamond substrates. (a) With an additional graphene layer and a PVD AIN layer underneath, the AIN and GaN can be grown on the diamond substrate in fixed in-plane orientation and the GaN layer becomes a uniformly distributed single-crystal continuous film. Reprinted with permission from Liu *et al.*, Adv. Funct. Mater. **32**, 2113211 (2022). Copyright 2022 Wiley-VCH.<sup>44</sup> (b) GaN growth on diamond substrates through series of buffer layers Reprinted with permission from Gao *et al.*, Mater. Des. **235**, 112444 (2023). Copyright 2023 Elsevier.<sup>44</sup>

#### B. $\beta$ -Ga<sub>2</sub>O<sub>3</sub> growth

(111) Diamond

β-Ga<sub>2</sub>O<sub>3</sub> boasts an ultrawide bandgap of almost 4.6–4.9 eV, contributing to its high critical electric field.<sup>3</sup> The most advantageous feature of β-Ga<sub>2</sub>O<sub>3</sub> is its sizable, scalable, and potentially cost-effective substrate. Moreover, β-Ga<sub>2</sub>O<sub>3</sub> can be *n*-type doped to achieve a low resistivity of approximately 1 mΩ·cm.<sup>46</sup> The challenge of introducing a *p*-type component may potentially be addressed through integration with heterojunctions, a concept encouraged by the recent demonstration of *p*-NiO/*n*-Ga<sub>2</sub>O<sub>3</sub> *p*-*n* heterojunctions with avalanche robustness.<sup>46</sup> This unique combination of large-size bulk availability and doping feasibility has sparked significant interest in the rapidly growing field of power electronics.

In contrast to other ultrawide bandgap semiconductors, singlecrystal gallium oxide can be grown using the melt method, which eliminates the need for extreme growth pressure. Since Ga<sub>2</sub>O<sub>3</sub> features multiple polymorphs, the growth of other polymorphs of Ga<sub>2</sub>O<sub>3</sub> also attracts numerous research interest.<sup>47</sup> The primary challenge of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> lies in its low and anisotropic thermal conductivity, leading to severe overheating issues in power devices. This intrinsic limitation in thermal conductivity, governed by intrinsic phonon properties, cannot be improved by growing high-quality crystals. As a potential solution, the epitaxial growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films on high thermal conductivity materials such as SiC and diamond emerges as a promising approach to mitigate overheating problems in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices.<sup>48–52</sup>

#### C. AIN growth

AlN stands out as a promising ultrawide bandgap semiconductor with wide-ranging applications in electronics and optoelectronics due to the large bandgap and high critical electric field.<sup>27</sup> Notably, recent advancements include substantial bulk *p*-type doping of AlN using beryllium, as well as a dopant-free AlN-based p-n junction diode, thereby elevating AlN to the status of a genuine semiconductor<sup>27,53</sup>

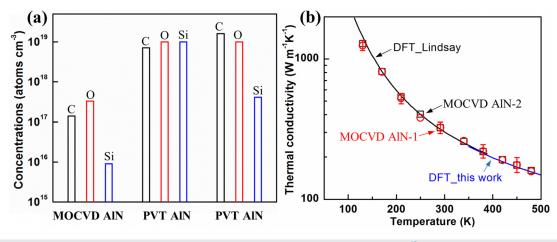

Bulk AlN wafers are typically grown by the physical vapor transport (PVT) technique. Second ion mass spectroscopy (SIMS) measurements reveal that there exist high concentrations  $(10^{19} \text{ atoms per cm}^3)$  of impurities such as carbon, oxygen, and silicon in bulk AlN wafers, as illustrated in Fig. 4(a).<sup>10</sup> Recent developments in the epitaxial

FIG. 4. Intrinsic high thermal conductivity of AIN. (a) SIMS data of impurity concentrations in MOCVD AIN and PVT AIN.<sup>10</sup> (b) Temperature-dependent thermal conductivity of high-quality MOCVD AIN. The experimentally measured thermal conductivity matches well with DFT-calculated values of single-crystal AIN. Reprinted with permission from Cheng *et al.*, Phys. Rev. Mater. **4**, 044602 (2020). Copyright 2020 American Physical Society.<sup>10</sup>

growth of thick AlN crystals on sapphire substrates via metal-organic chemical vapor deposition (MOCVD) have yielded crystals with high purity. This improved purity in AlN contributes to a substantial increase in thermal conductivity, reaching 321 W m<sup>-1</sup> K<sup>-1</sup> at room temperature, as depicted in Fig. 4(b).<sup>10</sup> Significantly, the measured cross-plane thermal conductivity of high-purity AlN grown by MOCVD aligns excellently with theoretical values calculated for single-crystal AlN using DFT. The dislocation densities of both samples are not high enough to affect the cross-plane thermal conductivity but may have an impact on the in-plane thermal conductivity.<sup>10,54,55</sup> Due to the hetero-epitaxial growth, the MOCVD-grown AlN on

sapphire has a higher density of dislocations than the bulk AlN crystals grown by PVT.

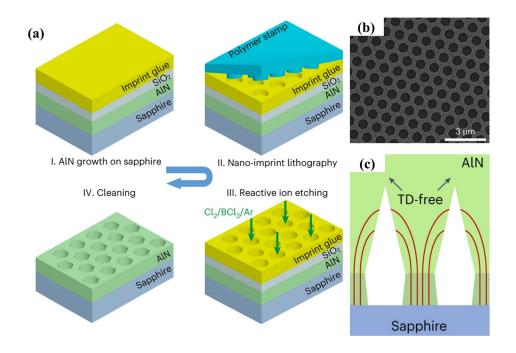

To further enhance the quality of AlN, there is a renewed focus on selective area growth, a traditional growth technology renowned for its efficacy in producing high-quality crystal thin films.<sup>56</sup> This approach seeks to achieve a low dislocation density, comparable to that found in native bulk substrates. In the case of AlN, the selective area growth of AlN islands is meticulously controlled to facilitate coalescence without the formation of new threading dislocations (TDs) after coalescence, utilizing nano-patterned sapphire substrates, as illustrated in Fig. 5.

**FIG. 5.** Selective area growth of highquality AIN (AIN film growth on NPATs). (a) The fabrication of NPATs. (b) The TEM image of the surface of NPATs with periodic hexagonal holes. (c) The evaluation of TDs in AIN films grown on NPATs. Reprinted with permission from Wang *et al.*, Nat. Mater. **22**, 853 (2023). Copyright 2023 Springer Nature.<sup>56</sup>

The fabrication of nano-patterned AlN/sapphire templates (NPATs) involves the use of reactive ion etching (RIE) to etch the AlN layer grown on sapphire with the aid of nano-imprint lithography. A transmission electron microscope (TEM) is employed to scrutinize the surface structure. The periodic hexagonal holes in the substrates reduce the density of threading dislocations (TDs) significantly, resulting in high-quality AlN.<sup>5</sup> The thermal conductivity of the high-quality AlN would further approach the theoretical values, especially for the inplane thermal conductivity, which are impacted strongly by the density of dislocations.

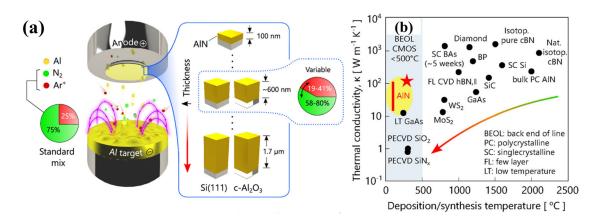

Emerging cooling techniques such as top-side cooling involve the deposition of materials with high thermal conductivity onto electronic device surfaces, which limits the deposition temperature to be lower than 400 °C. However, the synthesis of high-quality crystals that have superior thermal conductivity typically necessitates high-temperature conditions. Consequently, there is a growing demand for high thermal conductivity dielectric materials that can be deposited at low temperatures. Figure 6(a) illustrates a schematic diagram of the growth of crystalline AlN via sputtering at room temperature.<sup>6</sup> Remarkably, the polycrystalline AlN thin films demonstrate thermal conductivities surpassing 100 W m<sup>-1</sup> K<sup>-1</sup>, as evidenced in Fig. 6(b). Figure 6(b) also encapsulates a comparison of deposition temperatures against the thermal conductivity of various high thermal conductivity materials. A notable trend is observed: as deposition temperatures decrease, crystal quality diminishes, leading to a corresponding reduction in thermal conductivity. Within the constraints of back-end-of-line (BEOL) compatible temperatures, AlN exhibits the highest thermal conductivity within sub-micrometer thickness ranges.

#### D. Digital alloys and superlattices

The growth of AlN/GaN and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> alloys and superlattices can be precisely controlled in chemical vapor deposition (CVD) or molecular beam epitaxy (MBE) growth processes. Figure 6 illustrates the successful growth of single monolayer (ML) AlN and GaN. Due to the absence of crystal symmetry, the atoms forming the atomic layer in two opposite directions parallel to certain crystal axes have different sequences. GaN, AlN, and their ternary alloys exhibit spontaneous polarization, leading to polarization-induced fixed charges and mobile carriers at the heterointerface, commonly known as a two-dimensional electron gas (2DEG) or two-dimensional hole gas (2DHG).<sup>58</sup> If these heterointerfaces are densely aligned, as seen in atomically thin superlattices composed of alternating layers of AlN and GaN, known as digital alloys (DAs), there might be an overlap of the 2DEG across layers, resulting in an extended carrier distribution. Notably, electrons in such atomically ordered compounds, like super-lattices, do not experience alloy scattering. Consequently, these super-lattices could provide a practical way to enhance the mobility of AlGaN, particularly at an Al composition where impurity doping is ineffective.

Structured digital alloys show significant promise for improving the performance of light-emitting diodes and power electronics. Furthermore, in the case of a compositional graded AlGaN, the distribution gradient of the polarization field can generate fixed charges and mobile carriers (occasionally addressed as three-dimensional electron gas or hole gas), such bulk doping methodology, referred to as distributed polarization doping (DPD), is characterized by its impurity-free feature which does not require thermally ionization energy.<sup>59</sup> This impurity-free feature is a promising approach for doping ultrawide bandgap materials like AlN and high Al-content AlGaN, addressing challenges posed by deep impurity levels. Recently, Wang et al. reported the discovery of superlattices between GaN and Mg, referred to as Mg-intercalated GaN superlattices (MiGs).<sup>60</sup> They achieved this by depositing a metallic Mg thin film onto bulk single-crystal GaN, followed by annealing the sample under atmospheric pressure. This straightforward and accessible process leads to the diffusion of Mg atoms into the GaN substrate as single-atomic layers. The incorporation of Mg induces significant variations in the GaN lattice constant and introduces considerable strain within the structure, potentially increasing the thermal conductivity, which requires further investigation. P-type GaN can be easily achieved by optimizing the annealing temperature.

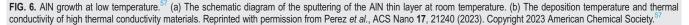

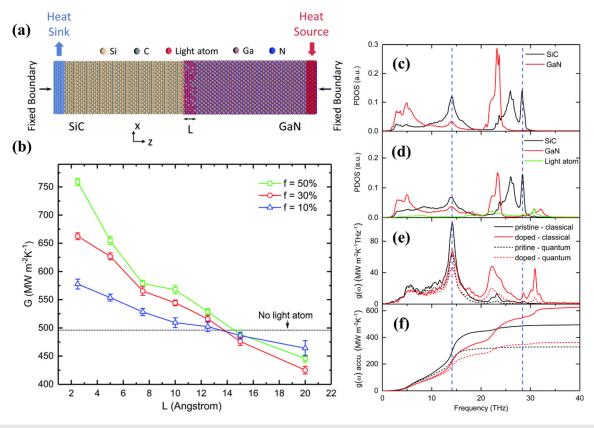

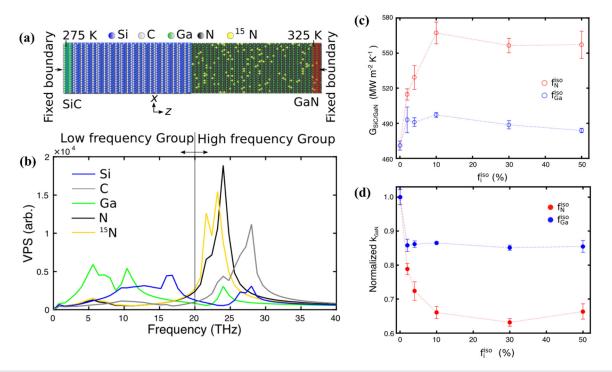

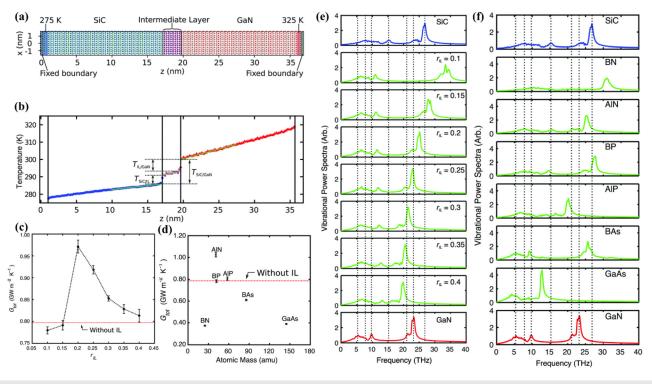

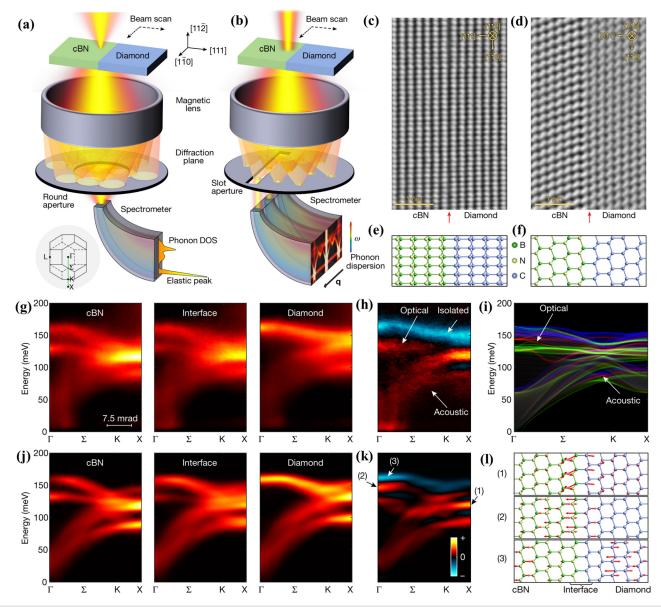

Contrary to their electrical properties, digital alloys and superlattices exhibit a strong reduction in thermal conductivity due to alloy scattering and boundary scatterings of phonons. Figures 7(a), 7(b), and 7(e) depict recent progress in the growth of ultrathin layers of GaN or

**FIG. 7.** Digital alloys and superlattices of AIN and GaN,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, and Al<sub>2</sub>O<sub>3</sub>. (a) The cross-sectional TEM images of digital alloyed (AIN)<sub>8</sub>/(GaN)<sub>2</sub> structure growth by metalorganic vapor phase epitaxy method. Reprinted with permission from Gao *et al.*, Cryst. Growth Des. **19**, 1720 (2019). Copyright 2019 American Chemical Society.<sup>61</sup> (b) A monolayer of GaN grown between AIN layers on the c-plane. Reprinted with permission from Wu *et al.*, Proc. Natl. Acad. Sci. U. S. A. **120**, e2303473120 (2023). Copyright 2023 National Academy of Sciences.<sup>62</sup> (c) and (d) The high-angle annular dark field-scanning transmission electron microscopy (HAADF-STEM) image of a  $\beta$ -(Al<sub>0.1</sub>Ga<sub>0.9</sub>)<sub>2</sub>O<sub>3</sub>/ Ga<sub>2</sub>O<sub>3</sub> superlattice structure and its thermal conductivity compared to the bulk  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as functions of temperature. Reprinted with permission from Cheng *et al.*, Appl. Phys. Lett. **115**, 092105 (2019). Copyright 2019 AIP Publishing LLC.<sup>22</sup> (e) The HAADF image of an AIN-(Al<sub>0.65</sub>Ga<sub>0.35</sub>)N superlattice structure. Reprinted with permission from Hoglund *et al.*, Adv. Mater. **36**, 2402925 (2024). Copyright 2024 John Wiley and Sons.<sup>63</sup>

AlGaN down to one or two monolayers. Furthermore, thermal studies are necessary to understand thermal transport in these new structures. Figure 7(d) demonstrates the measured thermal conductivity of  $\beta$ -(Al<sub>0.1</sub>Ga<sub>0.9</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> superlattice, which is approximately five times lower than that of the corresponding bulk crystal.<sup>22</sup> The layered structure of digital alloy and superlattices displays anisotropic thermal conductivity, with in-plane thermal conductivity significantly higher than cross-plane thermal conductivity.

Recently, the incorporation of scandium (Sc) has significantly increased the spontaneous polarization of AlN, propelling AlN/AlScN heterostructures to the forefront of research.<sup>64</sup> Additionally, other elements are proving to be influential within this context. Examples include AlPN/GaN,<sup>65</sup> AlBN/AlN,<sup>66</sup> and quinary AlScYLaN/AlN heterostructures.<sup>67</sup> B enhances the dielectric constant of AlN, while Sc, Y, and La boost its ferroelectric properties. Thus, the alloying of AlN with these elements offers extensive opportunities to modulate its electrical properties, unlocking the vast potential of AlN-based heterostructure systems. However, a drawback is that thermal conductivity tends to diminish with the introduction of additional alloying elements, potentially leading to overheating issues in electronic applications.

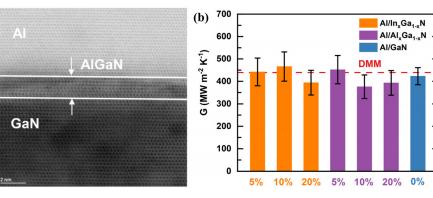

The adjustment of a certain component's composition can result in variations in the phonon properties of the structure. In a recent study, the proportions of Ga and Al or Ga and In in the alloy  $In_xGa_{1-x}N$  or  $Al_xGa_{1-x}N$  were modified.<sup>68</sup> The fraction x ranged from 5% to 20%, and this material served as an interlayer between Al and GaN. By controlling the composition of Al or In atoms, the impact on TBC was investigated, as depicted in Fig. 8. Figure 8(a) presents a TEM image of the fabricated interface, clearly illustrating the presence of an interlayer. The TBC values observed under various compositions are shown in Fig. 8(b). However, the discernible effect of composition on the TBC of this structure warrants further investigation.

#### E. SiC growth

Silicon carbide has about 250 crystalline polytypes. The 4H-SiC and 6H-SiC have been widely applied in power electronics as active components or substrate materials. The commercially available high-quality wafers have achieved intrinsic high thermal conductivity which agrees with first-principal calculations.<sup>6,36,37</sup> The massive production also leads to stable crystalline quality of wafers up to 8 in. size. The large wafer size facilitates cost reduction in related electronics. Due to the expensive cost of ultrahigh purity SiC, smart-cut techniques have been developed to bond highpurity SiC on low-quality SiC substrates to form composite wafers. Most studies focus on homo-epitaxy since hetero-epitaxy of 4H-SiC and 6H-SiC are still challenging. The effects of structural imperfections such as defects or dislocations on thermal conductivity are much less studied than those on electrical properties. The understanding of defect-phonon scattering and electron-phonon scattering in 4H-SiC and 6H-SiC crystalline is still very limited.<sup>6</sup>

The cubic phase of silicon carbide (3C-SiC) has been less explored experimentally, compared to its hexagonal counterparts, namely, 4H-SiC and 6H-SiC, primarily due to the scarcity of highquality and pure wafers. Recent theoretical calculations suggest that the 3C-SiC has the highest intrinsic thermal conductivity among all

(a)

**Applied Physics Reviews**

**FIG. 8.** The regulation of the material composition of the interlayer. (a) The TEM image of the GaN/AI interface and the Al<sub>x</sub>Ga<sub>1-x</sub>N interlayer. (b) TBCs of different interlayers of different material compositions. Reprinted with permission from Li *et al.*, J. Appl. Phys. **134**, 230901 (2023). Copyright 2023 AIP Publishing LLC.<sup>66</sup>

SiC polytypes (exceeding 500 W m<sup>-1</sup> K<sup>-1</sup>). However, historically, the measured thermal conductivity in the literature was about 50% lower than the theoretical predictions.<sup>70</sup> This discrepancy was attributed to the presence of impurities or grain boundaries within the studied 3C-SiC crystals.<sup>70</sup> In particular, boron impurities was identified as potent phonon scatterers, significantly diminishing thermal conductivity beyond even the effects of vacancies.<sup>70</sup>

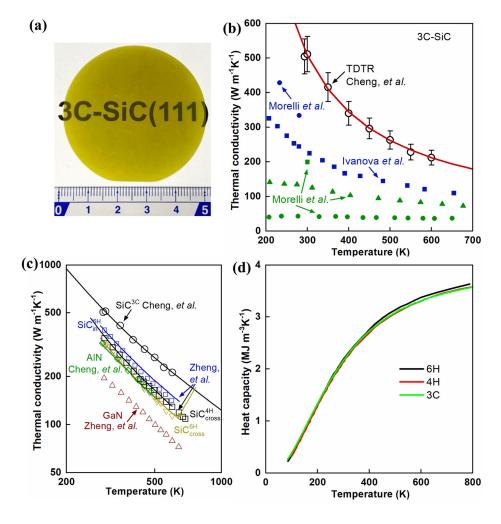

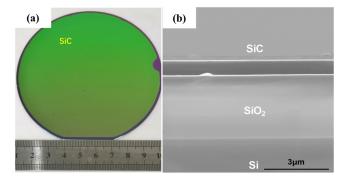

High-purity and high-quality 3C-SiC crystals have recently been demonstrated to have a high thermal conductivity exceeding 500 W  $m^{-1} K^{-1,71}$  Figure 9(a) presents the picture of high-quality and high-purity 3C-SiC wafer grown by CVD in a customized chamber.<sup>7</sup> The freestanding 3C-SiC single-crystal wafer is fabricated by initially growing a thick layer on a silicon substrate, followed by subsequent removal of the substrate through etching.<sup>7</sup> The measured thermal conductivity

FIG. 9. High thermal conductivity of waferscale 3C-SiC crystals. (a) Picture of a freestanding 3C-SiC wafer. (b) Experimentally measured high thermal conductivity of high-quality 3C-SiC matches well with DFT-predicted values of single-crystal 3C-SiC.<sup>7</sup> The literature data of measured thermal conductivity of 3C-SiC is also included for comparison. (c) The isotropic thermal conductivity of 3C-SiC is compared with other high thermal conductivity wafers (AIN, GaN, 4H-SiC, and 6H-SiC).6 Both the in-plane and cross-plane thermal conductivity of 6H-SiC are included since it is anisotropic.6 (d) Suggested data of volumetric heat capacity of 3C-SiC, 4H-SiC, and 6H-SiC.6, Reprinted with permission from Cheng et al., Nat. Commun. 13, 7201 (2022). Copyright 2022 Springer Nature.

of the high-quality and high-purity 3C-SiC closely aligns with theoretical predictions and markedly surpasses previously documented values, as depicted in Fig. 9(b).<sup>7</sup> Notably, the thermal conductivity of 3C-SiC ranks second only to diamond among large crystals; however, diamond's applications are hindered by its limited wafer size alongside its exorbitant cost and the challenges associated with semiconductor integration. In contrast, 3C-SiC can grow large wafers up to 8 in., which is important for massive production. Figure 9(c) illustrates the superior temperature-dependent thermal conductivity of 3C-SiC relative to 4H-SiC, 6H-SiC, GaN, and AlN single crystals across the measured temperatures.<sup>7</sup> Additionally, due to its cubic structure, 3C-SiC exhibits isotropic thermal properties, maintaining high thermal conductivity in both in-plane and cross-plane orientations. Moreover, there is a close concordance with minimal deviations observed in heat capacity data among 4H-SiC, 6H-SiC, and 3C-SiC, as demonstrated in Fig. 9(d).<sup>6,7</sup>

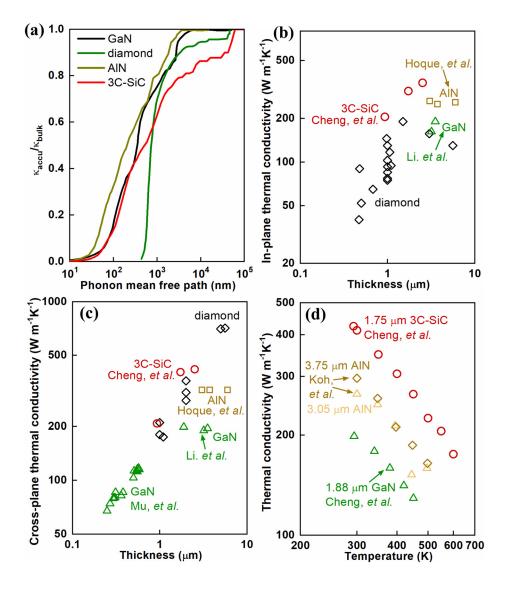

Figure 10(a) delineates the contribution of phonons with different mean free paths (MFP) to the thermal conductivity of thin films

normalized by their corresponding bulk counterparts.<sup>7</sup> Owing to the typically long phonon mean free paths in high thermal conductivity semiconductors, a pronounced size effect on the thermal conductivity of these thin films is anticipated. As integral elements of functional devices, the thermal conductivity of semiconductor thin films is of paramount importance. Figures 10(b) and 10(c) depict the thicknessdependent in-plane and cross-plane thermal conductivity of semiconductor thin films.<sup>7</sup> The data indicate that all examined (ultra)wide bandgap semiconductor thin films exhibit a significant dependence on film thickness regarding thermal conductivity. Notably, the measured thermal conductivity values of 3C-SiC thin films reach unprecedented high values in both in-plane and cross-plane dimensions, surpassing those of CVD diamond films of comparable thicknesses. Whereas the CVD diamond films formed on dissimilar substrates are polycrystalline or nanocrystalline, the AlN, GaN, and 3C-SiC thin films approach single-crystal quality. This highlights the grain boundaries within diamond films as contributors to phonon scattering, which moreover

FIG. 10. Thermal conductivity of waferscale thin films of high thermal conductivity materials. (a) Accumulated thermal conductivity of GaN, diamond, AIN, and 3C-SiC normalized by their corresponding bulk thermal conductivity. (b) Thicknessdependent in-plane thermal conductivity of (c) Thickness-dependent thin films. cross-plane thermal conductivity of thin films. (d) Temperature dependence of cross-plane thermal conductivity of thin films. Reprinted with permission from Cheng et al., Nat. Commun. 13, 7201 (2022). Copyright 2022 Springer Nature

Appl. Phys. Rev. 11, 041324 (2024); doi: 10.1063/5.0185305 Published under an exclusive license by AIP Publishing reduces the thermal conductivity. As illustrated in Fig. 10(d), the cross-plane thermal conductivity of thin films still exhibits a strong temperature dependence, with 3C-SiC outperforming other semiconductors across the observed temperature range.<sup>7</sup> Furthermore, 3C-SiC thin films can serve as substrates or transition layers for epitaxial growth of other semiconductors, such as AlN and GaN, given that 3C-SiC is the sole SiC polytype compatible with epitaxy on Si.<sup>75</sup> This compatibility also renders 3C-SiC-Si composite wafers a cost-effective alternative to bare SiC wafers.

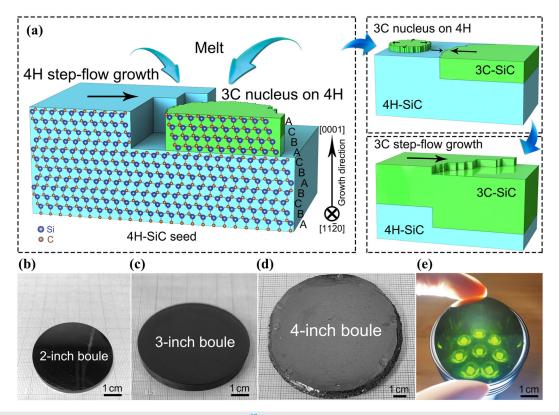

Crystals of 3C-SiC grown using CVD exhibit high thermal conductivity; however, their growth rate remained low, challenging the production of thick wafers. Recently, notable advancements have been achieved in the bulk synthesis of 3C-SiC atop 4H-SiC substrates,<sup>87</sup> as evidenced by Fig. 11. Optimizing nitrogen partial pressure above 15 kPa during the top-seated solution growth (TSSG) process has led to a favorable change in interfacial energies, thereby enhancing the formation of 3C-SiC compared to 4H-SiC. Such conditions facilitate the increased nucleation of 3C-SiC on the 4H-SiC seed surface and bolster the step-flow growth rate. These improvements not only promote the predominance of 3C-SiC crystal growth but also achieve high crystal quality and elevated growth rates. Figures 11(b)–11(e) display images of the resulting bulk single crystals of 3C-SiC. Although heavy nitrogen doping—at a scale of  $10^{20}$  cm<sup>-3</sup>—is essential for the crystallization process, it is noteworthy that such doping may considerably compromise thermal conductivity.

### III. HETEROGENEOUS INTEGRATION: BONDING WITH HIGH THERMAL CONDUCTIVITY MATERIALS

Despite significant strides in materials growth techniques leading to enhanced thermal conductivity, the demand for improved cooling solutions persists in device applications. Simply enhancing the quality of semiconductor materials falls short in adequately addressing the escalating thermal challenges confronting current and future semiconductor devices. In response to these limitations, semiconductor bonding techniques present effective solutions by capitalizing on the unique advantages of individual materials. Strategic bonding of two materials or wafers enables the full exploitation of their respective merits. Heterogeneous bonding emerges as a critical approach to harnessing the high thermal conductivity of materials such as SiC and diamond, as elaborated in Sec. II. In bonded structures, the thermal boundary conductance (TBC) between materials becomes a pivotal factor governing the extraction and dissipation of generated Joule heat, particularly in addressing hot spots.<sup>4,88-91</sup> Achieving a sufficiently high TBC, closely linked to the crystal structure near the interface and interlayer between materials, proves essential for successful thermal management during wafer bonding.<sup>4,91–94</sup> The interface structure intricately depends

**FIG. 11.** The process of 3C-SiC growth on the 4H-SiC seed by TSSG method.<sup>87</sup> (a) 3C-SiC nucleus on 4H-SiC seed while 4H-SiC is growing. However, more 3C-SiC nuclei on 4H-SiC seed overtake the growth under appropriate N<sub>2</sub> partial pressure. At last, the whole surface is covered by 3C-SiC. (b) and (c) The 2- and 3-in. 3C-SiC boule obtained by TSSG followed by rounded cutting. (d) The as-growth 4 in. 3C-SiC boule. (e) 3C-SiC single-crystal wafer showed green under strong light. Reprinted with permission from Wang *et al.*, Energy Environ. Mater. **7**, e12678 (2023). Copyright 2023 Wiley.<sup>6</sup>

REVIEW

pubs.aip.org/aip/are

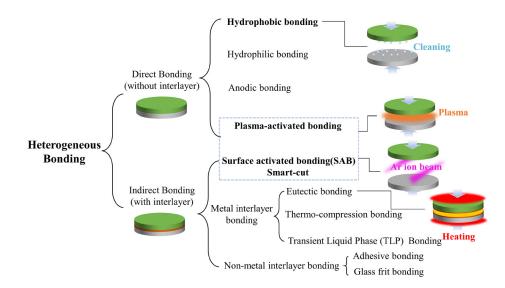

**FIG. 12.** The classification of different wafer bonding methods.

on the bonding methods forming the interface and subsequent postprocessing steps like annealing.<sup>86,89,95</sup> Conventional bonding methods fall into two categories: direct bonding, where no intentional interlayer is deposited between wafers before bonding, and indirect bonding, where an interlayer is deposited to enhance bonding or offer protection. A comprehensive classification is provided in Fig. 12. Notably, plasma bonding, surface-activated bonding (SAB), and smart-cut techniques can function as either direct or indirect bonding methods, depending on specific scenarios. This review primarily delves into hydrophilic bonding, plasma bonding, surface-activated bonding (SAB), and smart-cut techniques, commonly employed in (ultra)wide bandgap semiconductors.

#### A. Surface-activated bonding

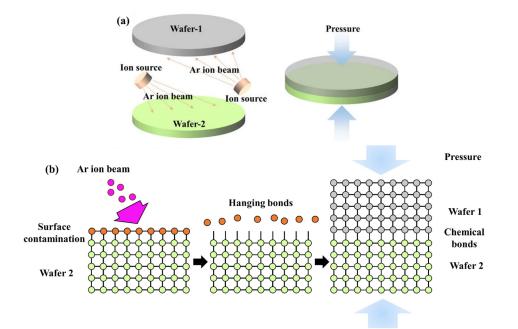

The surface-activated bonding (SAB) technique has attracted considerable attention in recent years amidst the increasing demand for heterogeneous integration. SAB, conducted at or near room temperature, effectively mitigates thermal stress near the bonding interface arising from mismatches in the coefficient of thermal expansion (CTE) between materials.<sup>96</sup> We will describe the SAB process and showcase notable examples of wafer bonding achieved through SAB in recent years.

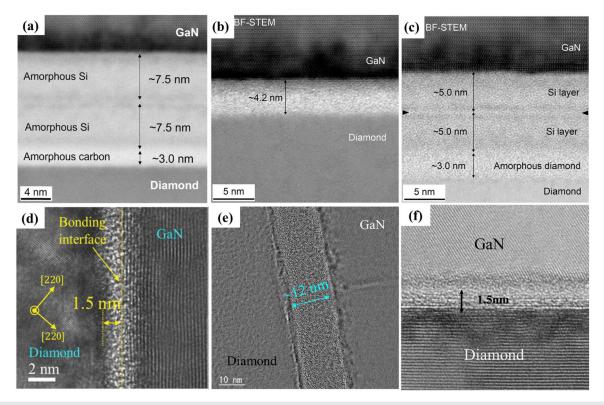

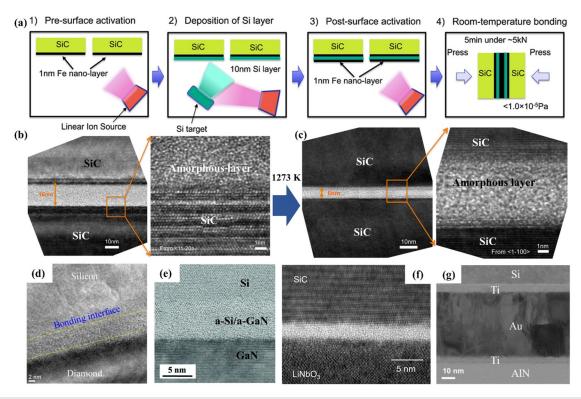

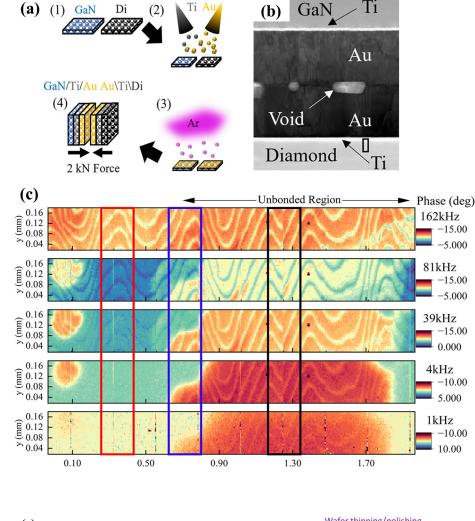

In the preparatory stage of SAB, the two wafers intended for bonding undergo chemical-mechanical polishing (CMP) to attain a surface roughness below 0.5 nm root mean square (RMS), a critical prerequisite for the subsequent bonding process. Following this, fast Ar ions are implanted onto the bonding surfaces to further eradicate surface contaminations and native oxide layers, ensuring an atomically clean surface to achieve sufficient bonding strength.<sup>97</sup> The two wafers are then brought together under pressure, as depicted in Fig. 13(a), whereby the dangling bonds generated during surface activation form chemical bonds to facilitate bonding, as illustrated in Fig. 13(b). All procedures are conducted at room temperature within a high vacuum environment. Although a thin layer near the bonding interface may incur damage from the Ar ion implantation, such effects can be mitigated through post-bonding annealing. Thanks to advancements in GaN growth technology, as discussed in Sec. II, and the refinement of device fabrication processes, GaNbased RF devices become ubiquitous in RF applications.<sup>98,99</sup> However, the high heat flux within the channel of GaN devices has significantly elevated the junction temperature, leading to increased instability in device performance and lifespan.<sup>18</sup> Therefore, integrating high thermal conductivity single-crystal diamond substrates with GaN devices has been proposed as an effective means to achieve near-junction cooling of GaN devices.<sup>100,101</sup> Utilizing the SAB method, GaNdiamond interfaces with high TBC can be achieved to fully exploit the advantages of diamond substrates. To ensure a strong and robust GaN-diamond interfaces, a layer of adhesion material is often applied before the bonding process. However, such layers may result in decreased TBC, as depicted in Figs. 14(a)–14(f).

In Fig. 14(a), both GaN and diamond wafers are pre-coated with an ultra-thin layer of Si to enhance bonding strength. However, this results in a thick interlayer of amorphous Si, significantly hindering heat transport across the interface.<sup>102</sup> Notably, a thin layer of diamond near the bonding interface turns into amorphous carbon due to Ar activation, while the GaN crystal structure remains intact. In contrast, Cheng et al. introduced Si into the Ar ion source, enabling simultaneous surface activation and Si interlayer deposition, resulting in a thin interlayer (only 4.2 nm) and a substantial increase in TBC, as shown in Fig. 14(b).<sup>86</sup> Comparatively, separately depositing Si would result in a thicker interlayer, as demonstrated in Fig. 14(c). Recently, new hybrid ion source of SiOx contained Ar has also been adapted by Xu et al., achieving an even thinner interlayer with a TBC as high as 120 MW m<sup>-2</sup> K<sup>-1,103</sup> The TBC in this study is highly sensitive to the thickness of the interlayer, which cannot be fully explained by the additional thermal resistance of the interlayer. Subsequent nonequilibrium molecular dynamics (NEMD) studies suggest that this is due to the mismatch of vibrational density of states (vDOS) between the mixture layer and the diamond or  $SiO_x$  layer.<sup>10</sup>

The absence of intentionally applied adhesion layers can lead to a thin amorphous interlayer, reducible through post-annealing, as depicted in Fig. 14(d).<sup>89</sup> Liang *et al.*, employing SAB, directly bonded a GaN layer onto a diamond substrate with an as-bonded interlayer of

**FIG. 13.** The procedure and principle of SAB. (a) The macroscopic procedure of SAB, including Ar ion implantation and the bonding of two wafers. Reprinted with permission from Cheng *et al.*, Appl. Phys. Lett. **120**, 030501 (2022). Copyright 2022 AIP Publishing LLC.<sup>90</sup> (b) The microcosmic principle of SAB. Dangling bonds created by the implantation of Ar ions form new chemical bonds under pressure near room temperature.

5.3 nm, reduced to 1.5 nm via 1000 °C annealing. Additionally, materials other than Si can serve as interlayers. For instance, Ayaka Kobayashi *et al.* deposited a SiC layer onto the diamond surface to reduce roughness,<sup>104</sup> shown in Fig. 14(e). Notably, after annealing, interlayer thickness may slightly increase due to the formation of extra SiC from Si and C atoms. Ar irradiation onto a Si substrate deposits an adhesion layer of only 1.5 nm onto the diamond surface, facilitating the achievement of an ultra-thin interlayer without the need for postannealing, as shown in Fig. 14(f).<sup>105</sup> While the thermal properties of this structure remain unstudied, a large TBC is anticipated.

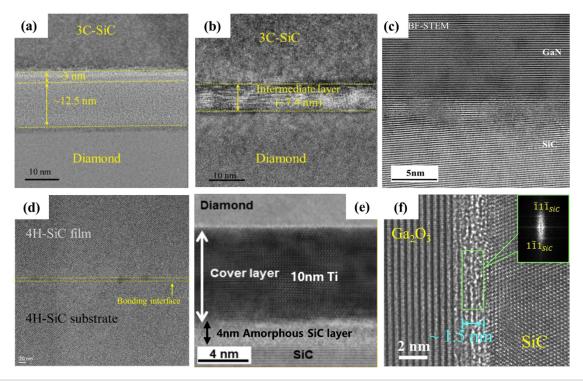

In addition to GaN/diamond interfaces, this review provides insights into several (ultra)wide bandgap semiconductor interfaces obtained through SAB, as depicted in Figs. 15–17, encompassing GaN/Si, GaN/SiC, SiC/SiC, 3C-SiC/diamond, 4H-SiC/diamond, Si/diamond, 3C-SiC/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, and AlN/Si interfaces.

Considering that 3C-SiC possesses a coefficient of thermal expansion (CTE) between that of diamond and GaN, along with a lattice constant close to that of GaN, and high thermal conductivity, Ryo Kagawa *et al.* utilized a 3C-SiC layer to construct a GaN/3C-SiC/diamond multilayer via SAB, buffering potential mismatches and stresses at the GaN/diamond bonding interface.<sup>97</sup> The as-bonded and postannealed interfaces at 1100 °C are depicted in Figs. 15(a) and 15(b), indicating that annealing significantly improves interfacial structure, reduces amorphous interlayer thickness, and enhances TBC, which is vital for device cooling. Another bonding of SiC and GaN wafers was performed by Mu *et al.* via SAB.<sup>85</sup> A significant increase in TBC and interlayer recrystallization were observed after annealing at 1273 K, as shown in Fig. 15(c).

In a recent study, Ma *et al.* demonstrated a homogeneous interface composed of 4H-SiC through SAB, which is shown in Fig. 15(d).<sup>106</sup> Post-annealing at 1973 K yielded an interface with a high TBC, suggesting great potential for SiC-based high-power devices.<sup>109</sup> A thick protective layer (10 nm Ti) was applied on the diamond interface to prevent damage from Ar ion beams by Minoura *et al.*<sup>107</sup> The image of the interface, depicted in Fig. 15(e), suggests the formation of a 4 nm thick amorphous SiC layer created by Ar ion implantation, while preserving the diamond's crystal structure under the Ti layer. The SiC wafer was then bonded to the bottom of an AlGaN/ GaN HEMT via SAB. Though the electrical performance of the HEMT improved, the TBC of the SiC/diamond interface was only 19 MW m<sup>-2</sup> K<sup>-1</sup>, possibly due to thick and amorphous interlayers.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, another important ultrawide bandgap semiconductor with low thermal conductivity, can also benefit from bonding. Liang *et al.* transferred a high thermal conductivity 3C-SiC thin film onto a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate and bonded them together via SAB.<sup>108</sup> TEM images of the bonded interface after 1000 °C annealing, as shown in Fig. 15(f), indicate reduced amorphous interlayer thickness due to recrystallization.

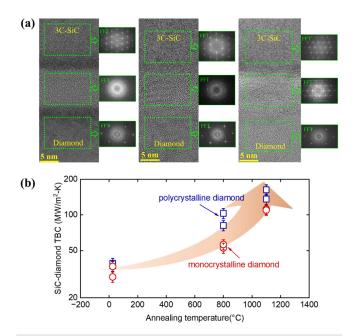

Recently, Cheng *et al.* reported that post-annealing facilitates TBC enhancement by chemical reaction at the interfaces.<sup>110</sup> TEM and FFT images of the bonded interface after annealing at different temperatures, as shown in Fig. 16(a), indicate chemical reaction of amorphous silicon with diamond to form SiC. The transition from SiC/Si/diamond into SiC/diamond leads to a record-high TBC enhancement for all bonded and grown interfaces after annealing. The bonded SiC/diamond TBC achieves a record-high value of 150 MW m<sup>-2</sup> K<sup>-1</sup> among all bonded diamond interfaces. The significantly increased TBCs after high-temperature annealing are illustrated in Fig. 16(b).

The schematic diagram of a modified SAB technique and additional bonded (ultra)wide bandgap semiconductor interfaces are shown in Fig. 17. Suga *et al.* employed a novel method of depositing Si interlayer by bombarding a Si target, depositing 10 nm thick Si layers onto both SiC wafers, followed by surface activation and pressing, as shown in Fig. 17(a).<sup>111</sup> The as-bonded interface, depicted in Fig. 17(b), shows a thick interlayer of amorphous Si. However, after annealing at 1273 K, the interlayer is reduced to 8 nm (half of the original value), as

FIG. 14. The GaN/diamond interfaces bonded by SAB. (a) the image of a GaN/diamond heterointerface with a ~15-nm-thick Si interlayer to enhance the bonding strength. Reprinted with permission from Mu *et al.*, J. Alloys Compd. **905**, 164076 (2022). Copyright 2022 Elsevier BV.<sup>102</sup> (b) The cross-sectional image of the GaN/diamond heterointerface with a thin interlayer obtained by Si-containing Ar ion beam. (c) The cross-section image of the GaN/diamond interface with a thick interlayer obtained by separately depositing Si. Reprinted with permission from Cheng *et al.*, ACS Appl. Mater. Interfaces **12**, 8376 (2020). Copyright 2020 American Chemical Society.<sup>86</sup> (d) The image of the GaN/diamond heterointerface after direct SAB and 1000 °C annealing. Reprinted with permission from Liang *et al.*, Adv. Mater. **33**, 2104564 (2021). Copyright 2021 Wiley-Blackwell.<sup>89</sup> (e) The image of 1000 °C-annealed GaN/diamond interface with a ~12 nm SiC layer to reduce the roughness of the diamond surface. Reprinted with permission from Matsumae *et al.*, Scr. Mater. **215**, 114725 (2022). Copyright 2022 Elsevier Ltd.<sup>105</sup>

shown in Fig. 17(c). Liang *et al.* achieved room-temperature bonding of Si/diamond interfaces via SAB, as depicted in Fig. 17(d).<sup>112</sup> This work also investigated the effect of annealing. After 1000 °C annealing, the amorphous interlayer recrystallizes, and forms SiC layer. In another similar study, Liang *et al.* fabricated a FET based on a SAB bonded Si/diamond structure.<sup>116</sup> After a 1000 °C-fabrication process, there is no abnormality in the electrical performance of the FET. Together with R. Kagawa *et al.*,<sup>95</sup> these results highlight that the electrical performance of a SAB-bonded interface is qualified for device fabrication. Additionally, Mu *et al.* realized room-temperature bonding of GaN/Si interfaces via SAB.<sup>113</sup> The GaN thin layers bonded to Si substrates at room temperature has sufficient bonding strength, feasible for subsequent device fabrication.<sup>117,118</sup> Though a 5-nm amorphous interlayer occurred, as shown in Fig. 17(e), its thickness may be further reduced by post-annealing.

Ryo Takigawa *et al.* directly bonded a LiNbO<sub>3</sub> wafer with SiC without interlayer deposition, as depicted in Fig. 17(f), resulting in an amorphous interlayer thickness less than 5 nm.<sup>114</sup> The room temperature bonding overcomes challenges posed by large CTE differences between SiC and LiNbO<sub>3</sub>, offering a potential solution to thermal issues in LiNbO<sub>3</sub>-based devices. AlN was also bonded to a Si wafer by

Matsumae *et al.* using SAB.<sup>115</sup> Different bonding conditions were tested, including direct bonding, Si adhesion layer bonding, and Au/Ti adhesion layer bonding, as shown in Fig. 17(g). The measurement of bonding strength under different conditions reveals that the direct bonded interface (0.93 J m<sup>-2</sup>) exhibits weaker bonding strength compared to interfaces with adhesion layers (>2.5 J m<sup>-2</sup>). This underscores the importance of interlayers to achieve sufficiently strong bonding, despite the potential hindrance they may pose to heat dissipation across the interface. In a similar work, Xu *et al.* achieved a directly bonded  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/SiC interface, demonstrating an average bonding energy of 2.31 J m<sup>-2</sup>. However, observation of Ga and Si diffusion near the interface due to the annealing process suggests the need for further study.<sup>119</sup>

#### B. Smart-cut technique

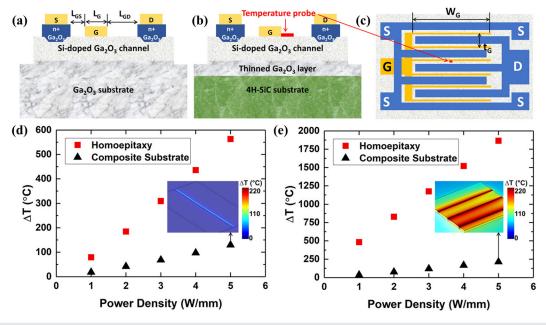

A sufficiently thin device layer on a substrate is crucial for effective thermal management, offering low thermal resistance between the junction and the substrate. This method can be particularly beneficial for materials like  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, which possesses relatively low thermal conductivity. The self-heating effect in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices poses a significant limitation in device performance. The integration of a nanoscale

FIG. 15. SAB bonding of some (ultra)wide bandgap semiconductors interfaces. (a) The image of the as-bonded 3C-SiC/diamond interface before annealing. (b) The image of the 3C-SiC/diamond interface after 1100 °C annealing. Reprinted with permission from Kagawa *et al.*, Small **20**, 2305574 (2023). Copyright 2023 Wiley-VCH Verlag.<sup>95</sup> (c) The image of GaN/SiC interface after annealed at 1273 K, with a crystallized interlayer. Reprinted with permission from Mu *et al.*, ACS Appl. Mater. Interfaces **11**, 33428 (2019). Copyright 2019 American Chemical Society.<sup>85</sup> (d) The image of the SiC/SiC interface. Reprinted with permission from Ma *et al.*, ACS Appl. Mater. Interfaces **11**, 33428 (2019). American Chemical Society.<sup>106</sup> (e) The image of a SiC/diamond interface with a 10-nm-thick Ti layer deposited on the diamond surface in advance for protection. Reprinted with permission from Minoura *et al.*, Jappl. Phys., Part **159**, SGGD03 (2020). Copyright 2020 Japan Society of Applied Physics.<sup>107</sup> (f) The image of the 3C-SiC/β-Ga<sub>2</sub>O<sub>3</sub> interface after 1100 °C annealing. Reprinted with permission from Liang *et al.*, arXiv:2209.05669 (2022). Copyright 2022 Author(s) under a CC BY 4.0 license.<sup>108</sup>

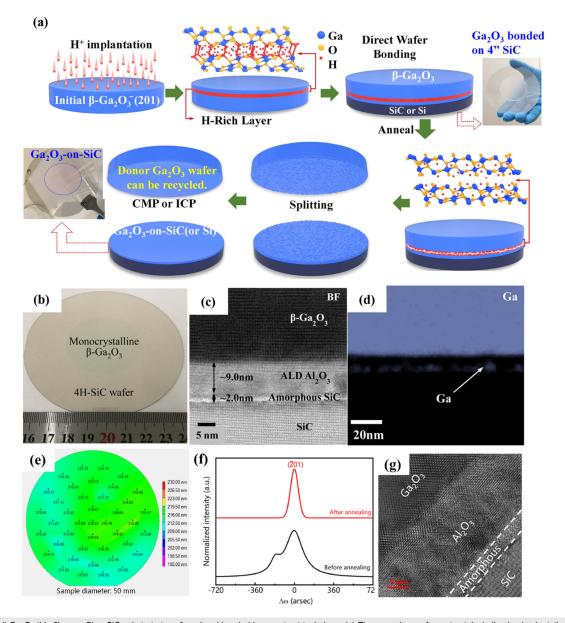

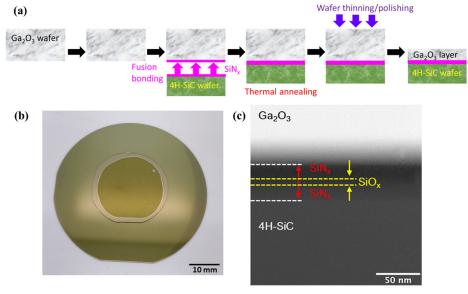

monocrystalline thin layer of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> onto a 4H-SiC substrate can be achieved through the smart-cut technique, outlined in Fig. 18(a).<sup>120,121</sup> First, H ions are implanted into the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> wafer, forming a H-rich layer underneath the surface. The wafer is then bonded onto a Si or SiC substrate using SAB. Subsequent annealing leads to the formation and growth of hydrogen gas bubbles at the H-rich layer, resulting in blistering,<sup>122–125</sup> and subsequently, exfoliation of the thin film bonded to the substrate. After polishing the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film and the substrate, the remaining  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> can be recycled for further use or fabrication.

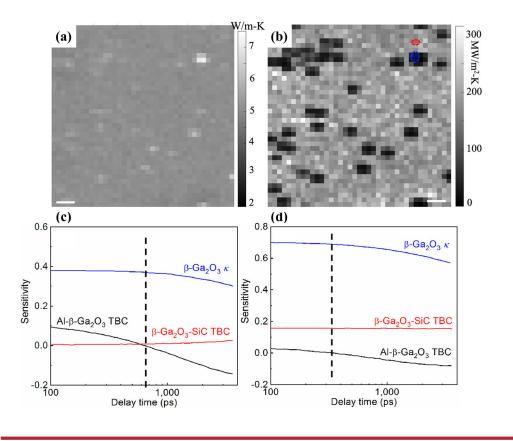

Cheng *et al.* conducted bonding of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films on 4H-SiC substrate through smart-cut, involving an Al<sub>2</sub>O<sub>3</sub> interlayer deposition via atomic layer deposition (ALD).<sup>24</sup> The transferred  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film on 4H-SiC exhibited excellent bonding quality, with a uniformly bonded interface. STEM imaging of the bonded interface after 800 °C annealing in N<sub>2</sub> revealed a slight decrease in the thicknesses of the ALD Al<sub>2</sub>O<sub>3</sub> interlayer and amorphous SiC layer, alongside improved crystalline quality of the Al<sub>2</sub>O<sub>3</sub> interlayer. Additionally, the annealing process relieved stress originating from ion implantation, thereby reducing phonon scattering and enhancing thermal conductivity. However, Ga diffusion due to the annealing process, alongside potential phonon scattering caused by alloy structure, may affect thermal transport across the interface. Xu *et al.* conducted mapping

quality, with a unionded interface after e in the thicknesses SiC layer, alongside er. Additionally, the n ion implantation, ng thermal conduc-

implantation.

films onto Si or SiC substrates through smart-cut to study the effects of interlayer and post-annealing processes.<sup>127</sup> These findings suggested that the Al<sub>2</sub>O<sub>3</sub> interlayer may help prevent element diffusion, resulting in high-quality  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films. Additionally, post-annealing processes were proven to recrystallize the interface structure and strengthen bonding strength.

of thickness across the entire bonding wafer, showing uniform thickness of the bonded  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film.<sup>121,126</sup> The normalized x-ray

diffractometer rocking curves (XRCs) of its (-201) plane after and

before a 900 °C annealing in  $O_2$  for 60 min is shown in Fig. 18(f).

The small full width at half maximum of the annealed XRCs indi-

cates that the annealing process can effectively improve the crystal

quality of the as-bonded thin film and recover the damage of ions

become amorphous after the bonding, but the amorphous layer at the

$\beta$ -Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> interface disappear after the annealing, which is shown

in Fig. 18(g). Subsequent experiments demonstrated a significant

decrease in device temperature based on such thin film, indicating the

Both the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> interface and Al<sub>2</sub>O<sub>3</sub>/SiC interface

pubs.aip.org/aip/are

**FIG. 16.** Bonded 3C-SiC/diamond interfaces with post-annealing process. (a) The TEM images and fast Fourier transform (FFT) images of the as-bonded, 800 °C-annealed, and 1100 °C-annealed interfaces. (b) The TBC increases with annealing temperate. Reprinted with permission from Cheng *et al.*, Adv. Electron. Mater. **2024**, 2400387. Copyright 2024 John Wiley and Sons.<sup>110</sup>

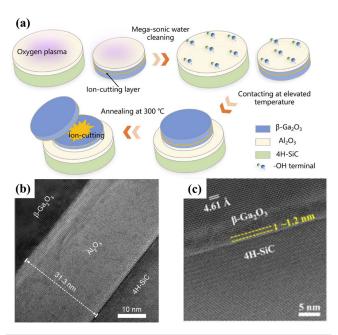

In addition to SAB, another room-temperature bonding method, hydrophilic bonding, can be utilized for bonding two wafers during the smart-cut process. The details and applications of hydrophilic bonding will be discussed in Sec. III C. Shen et al. achieved smart-cut through hydrophilic bonding, as depicted in Fig. 19(a).<sup>128</sup> However, to ensure sufficient bonding capable of withstanding high-temperature processes during thin film exfoliation, a thick adhesion layer of Al<sub>2</sub>O<sub>3</sub> was intentionally deposited on the surfaces of both wafers. As shown in Fig. 19(b), a  $\sim$ 30 nm thick layer of Al<sub>2</sub>O<sub>3</sub> introduces additional thermal resistance that requires further optimization. Xu et al. accomplished direct bonding of smart-cut  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on 4H-SiC by hydrophilic bonding.<sup>129</sup> In this study, no intentional interlayer was introduced, resulting in a thin amorphous interlayer, as illustrated in Fig. 19(c). Although further study on the thermal properties of these interfaces is needed, it is anticipated that interfaces with thin interlayers may exhibit high TBCs.

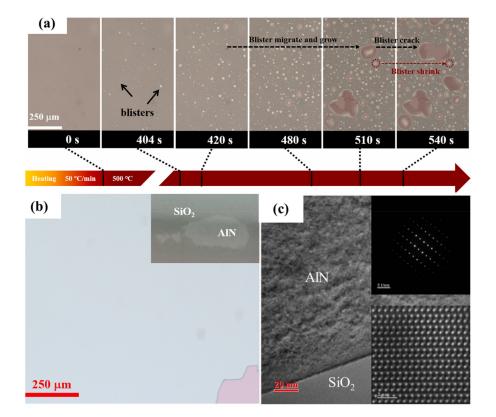

The transfer and bonding of a GaN layer onto a substrate by smart-cut has also been extensively studied.<sup>133–135</sup> Chung *et al.* bonded a GaN thin film onto sapphire using the smart-cut technique, followed by dry etching to remove the damage layer induced by H ions implantation.<sup>136</sup> A layer of MOCVD-GaN was epitaxially grown on the top of the GaN thin films after the bonding. The TEM images of the GaN without dry etching and the dry-etched GaN are shown in Figs. 20(a) and 20(d). The dry etching process effectively removed the damaged layer and result in high-quality GaN.

Shi *et al.* bonded a thin film of GaN to a  $SiO_2/Si$  substrate, as depicted in Fig. 20(b).<sup>131</sup> Meanwhile, the GaN near the interface is shown to have high quality, as shown in the area electron diffraction (SAED) pattern in the inset. The image of the bonded GaN-on-Si

wafer is shown in Fig. 20(c). Liu *et al.* achieved direct bonding of a GaN thin film onto a Si substrate without any intentionally deposited interlayer.<sup>132</sup> The TEM image of the bonded interface is shown in Fig. 20(e), where the GaN/Si interface is strongly bonded and only has a thin interlayer. Fig. 20(f) shows a thin layer of uniform ReS<sub>2</sub> grown on the top of GaN thin film for further device fabrication.

Qin *et al.* bonded a thin layer of AlN onto a Si substrate by the smart-cut method. Figure 21 shows the evaluation of the bubbles during the ion implantation and blistering process.<sup>137</sup> Figure 21(a) illustrates the evaluation of blister cracks over time, with bubbles enlarging and increasing in quantity, ultimately resulting in weak bonding near the ion-rich layer. Figure 21(b) shows the optical microscopy (OM) image of the bonded AlN surface, where no voids or cracks are observed. Figure 21(c) shows the TEM image of the AlN/SiO<sub>2</sub> interface, similar to the aforementioned GaN/Si structure. The thick SiO<sub>2</sub> isolator layer is from the thermal oxide layer on the Si substrate.

Due to the high cost of high-quality SiC, the smart-cut technique is used to fabricate high-quality SiC thin films bonded on low-cost substrates. The high-quality SiC thin films can be used for further device fabrication similar to those on the bulk high-quality SiC substrate.<sup>139</sup> Yi *et al.* bonded a 4H-SiC thin film onto a SiO<sub>2</sub>/Si substrate by smartcut technique.<sup>138</sup> Figure 22(a) shows the bonded 4H-SiC thin film on SiO<sub>2</sub>/Si wafer. No obvious voids or cracks are observed, indicating a uniform bonding. Figure 22(b) shows the TEM image of the SiC/SiO<sub>2</sub>/ Si interface. Sharp interfaces can be observed and no defects or damage were found in the 4H-SiC layer.

Most smart-cut semiconductor heterostructures mentioned above lack experimental measurements of their thermal properties, such as thermal conductivity and TBC between the films and substrates. Therefore, this area warrants further investigation. For the structures involving thick  $SiO_2$  layers, <sup>131,137,138</sup> such thick layer of low thermal conductivity material is expected to seriously hinder thermal transport between the device layer and the substrate. Efforts should be made to reduce the thickness of the isolator layer while minimizing its impact on device performance.

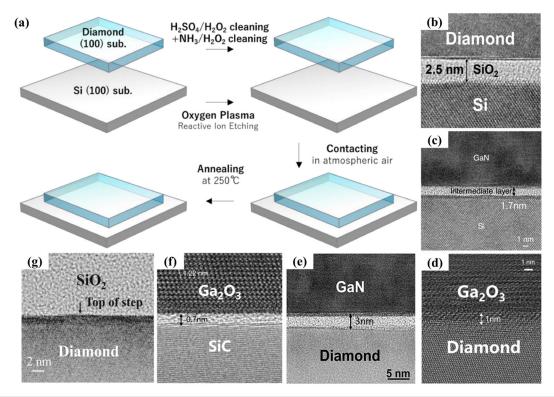

#### C. Hydrophilic bonding

In addition to SAB, hydrophilic bonding emerges as another crucial technique for integrating (ultra)wide bandgap semiconductors, potentially offering high TBC due to the presence of thin interfacial layers. Similar to SAB, the surfaces of the two to-be-bonded wafers must undergo polishing, achieving a surface roughness below 0.5 nm (RMS). Subsequently, the diamond substrate undergoes a cleaning process using H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub> and NH<sub>3</sub>/H<sub>2</sub>O<sub>2</sub> solutions, while the Si substrate is treated by oxygen plasma in reactive ion etching (RIE). Following these preparations, the two wafers are pressed together at atmospheric air and annealed at 250 °C, as depicted in Fig. 23(a).<sup>14</sup> Cross-sectional TEM images of bonded interfaces through the hydrophilic bonding technique, such as Si/diamond, GaN/Si, β-Ga<sub>2</sub>O<sub>3</sub>/diamond, GaN/diamond,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/SiC, and SiO<sub>2</sub>/diamond interfaces, are presented in Figs. 23(b)-23(g). In contrast to the aforementioned SAB techniques, which require a vacuum bonding environment, hydrophilic bonding circumvents such extreme processes and conditions, minimizing damage to the crystal structure. Figure 23(b) shows an interface between diamond and Si attained by hydrophilic bonding.<sup>141</sup> This structure did not undergo Ar ions activation. As a result, a thin interlayer of 2.5 nm SiO<sub>2</sub> appeared, which is thinner compared to the

FIG. 17. Other (ultra)wide bandgap semiconductor interfaces bonded by SAB. (a) A modified SAB method which deposits Si interlayer by Ar ion sputtering. (b) The image of the as-bonded SiC/SiC interface with a thick amorphous interlayer. (c) The image of the SiC/SiC interface after annealing at 1273 K, which indicates the decrease in the amorphous interlayer's thickness. Reprinted with permission from Suga *et al.*, Jpn. J. Appl. Phys., Part 1 **54**, 030214 (2015). Copyright 2015 IOP Publishing.<sup>111</sup> (d) The image of a 800 °C-annealed direct bonding Si/diamond interface. Reprinted with permission from Liang *et al.*, Diamond Relat. Mater. **93**, 187 (2019). Copyright 2019 Elsevier BV.<sup>112</sup> (e) The image of directly bonded Si/GaN interface with amorphous Si and GaN interlayer. Reprinted with permission from Mu *et al.*, Appl. Surf. Sci. **416**, 1007 (2017). Copyright 2020 Elsevier.<sup>113</sup> (f) The image of a SiC/LiNbO<sub>3</sub> interface fabricated by SAB. Reprinted with permission from Takigawa *et al.*, Scr. Mater. **174**, 58–61 (2020). Copyright 2020 Elsevier.<sup>114</sup> (g) The image of a AIN/Si interface sobtained by SAB with a Ti/Au/Ti interlayer. Reprinted with permission from Matsumae *et al.*, Ceram. Int. **46**, 25956–25963 (2020). Copyright 2020 Elsevier.<sup>115</sup>

as-bonded SAB interlayer mentioned above. Several studies have been carried out on the room-temperature hydrophilic bonding of diamond/Si interface.<sup>142–145</sup> Most of them show high quality bonding of crystals with a thin interlayer, which highlights the feasibility of hydrophilic bonding. Other pairs of interfaces bonded by hydrophilic bonding are GaN/Si in Fig. 23(c), Ga<sub>2</sub>O<sub>3</sub>/diamond in Fig. 23(d), GaN/diamond in Fig. 23(e), Ga<sub>2</sub>O<sub>3</sub>/diamond in Fig. 23(f), and SiO<sub>2</sub>/diamond in Fig. 23(g).<sup>140,141,146–150</sup> Thin interlayers and highcrystal quality are found among these structures. Although thermal characterizations are still lacking, these interfaces are expected to have high TBC due to the well-structured interface. However, a drawback of the hydrophilic bonding technique is the instability of bonded interfaces at high temperatures. For real-world applications, devices need to be fabricated first and then bonded with other materials. The uniformity of bonded interfaces over a large area also requires further investigation.

#### D. Plasma bonding

Plasma bonding is another robust bonding method capable of forming strong bonds.<sup>154</sup> The mechanism of plasma bonding shares similarities with SAB. SAB employs surface activation achieved

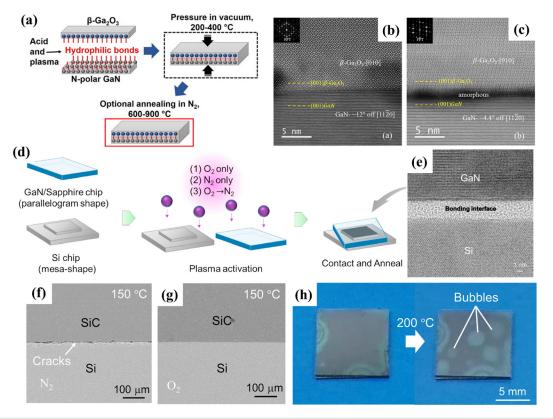

through Ar ion implantation, while plasma bonding utilizes Ar, O<sub>2</sub>, or  $N_2$  plasma.<sup>155</sup> Jian *et al.* conducted plasma bonding of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN interface.<sup>151</sup> As illustrated in Fig. 24(a), atomically smooth surfaces of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and GaN were activated by acid and atmospheric plasma, followed by bonding the two wafers under pressure without depositing an interlayer. The TEM image of the as-bonded interface [Fig. 24(b)] reveals no voids. However, an amorphous interlayer appeared when the structure underwent 900  $^\circ \mathrm{C}$  annealing in  $\mathrm{N}_2$  , necessitating further investigation. Matsumae et al. explored the effect of O2 and N2 used during surface activation in plasma bonding of GaN and Si.152 Different activation conditions were tested, as depicted in Fig. 24(d). The results indicated that, for bonding of GaN and Si, single use of O2 or N<sub>2</sub> failed to form sufficiently strong bonds; only sequential plasma activation led to strong adhesion, as evidenced by the TEM image of the interface [Fig. 24(e)]. Another study focused on the effect of plasma components was conducted by Kang *et al.*<sup>153</sup> Figures 24(f) and 24(g) are the TEM images of two interfaces bonded in N2 plasma and O2 plasma after annealing at 150 °C. It shows that only O<sub>2</sub> plasma can form a uniform interface without voids and cracks. However more bubbles area would form in the interface in O2 atmosphere, as shown in Fig. 24(h).

pubs.aip.org/aip/are

**FIG. 18.** The  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films on Si or SiC substrate transferred and bonded by smart-cut technique. (a) The procedures of smart-cut, including ion implantation, SAB, exfoliation, and polishing. Reprinted with permission from Li *et al.*, Fundam. Res. (published online) (2023). Copyright 2023 Elsevier.<sup>121</sup> (b) A thin film of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transferred on a 4 in. 4H-SiC wafer. (c) The STEM image of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-SiC interface after annealing. (d) The Ga distribution near the bonded interface after annealing obtained by EELS, indicating the diffusion of Ga. Reprinted with permission from Cheng *et al.*, ACS Appl. Mater. Interfaces **12**, 44943 (2020). Copyright 2020 American Chemical Society.<sup>24</sup> (e) The thickness variation of a 2 in.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film. (f) The XRCs of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film after and before a 450 °C annealing process. (g) The image of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SiC interface with permission from Li *et al.*, Fundam. Res. (published online) (2023). Copyright 2023 Elsevier.<sup>121</sup>

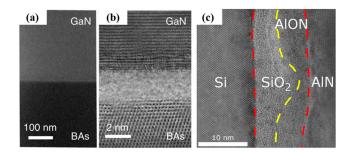

Kang *et al.* fabricated a GaN/BAs interface by plasma bonding with an  $Al_2O_3$  interlayer deposited by ALD. SEM and TEM images of the bonded interface after a 773 K annealing showed a 2-nm-thick interlayer, as illustrated in Figs. 25(a) and 25(b).<sup>156</sup> The TBC of this interface was measured to be 250 MW m<sup>-2</sup> K<sup>-1</sup>, much higher than the TBC of the diamond/GaN interface, attributed to the better matching of the

phonon dispersion relations of BAs and GaN.<sup>156</sup> Nieminen *et al.* bonded an AlN wafer onto a Si wafer through plasma bonding.<sup>157</sup> A 10-nm oxide multilayer appeared at the interface, as shown in Fig. 25(c). The TBC of this interface was measured to be 105 MW m<sup>-2</sup> K<sup>-1</sup>, even larger than the deposited AlN/Si interface in the same study. The authors attributed this high TBC to the high quality of the adhesive interlayer.

**FIG. 19.** Smart-cut achieved by hydrophilic bonding process. (a) The procedure. (b) The image of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/4H-SiC interface with a thick interlayer. Reprinted with permission from Shen *et al.*, Sci. China Mater. **66**, 756–763 (2023). Copyright 2023 Springer Nature.<sup>128</sup> (c) The TEM image of another hydrophilic bonding smart-cut  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/4H-SiC interface without intentionally deposited interlayer. Reprinted with permission from Xu *et al.*, Appl. Phys. Lett. **124**, 112102 (2024). Copyright 2024 AIP Publishing LLC.<sup>28</sup>

#### E. Other bonding methods

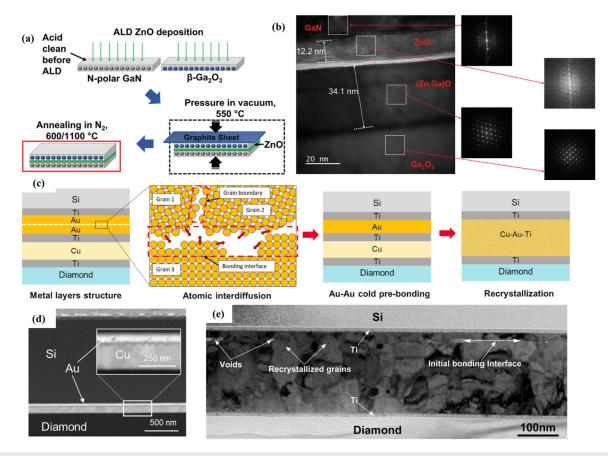

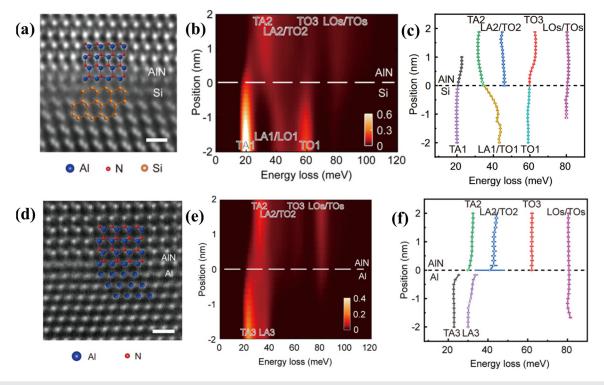

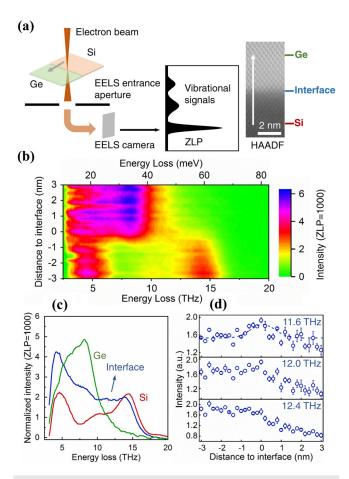

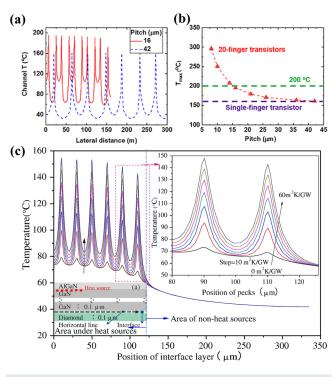

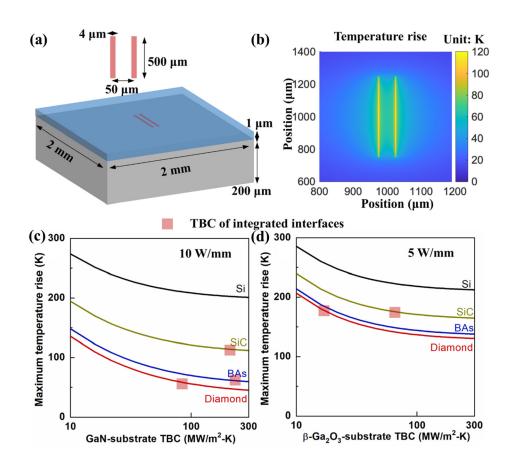

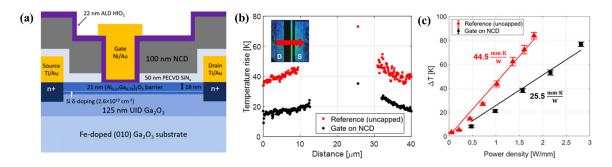

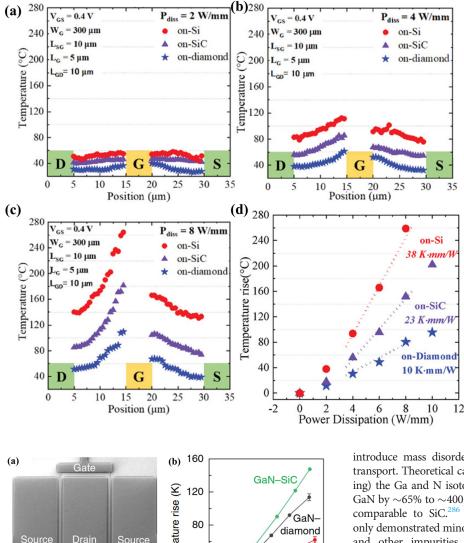

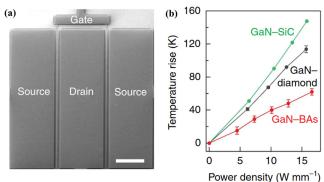

Jian et al. demonstrated the bonding of a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN interface through the diffusion of a ZnO layer deposited by ALD. The procedure is depicted in Fig. 26(a). After high temperature and pressure, ZnO diffused into the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer, as shown in Fig. 26(b). The adhesive ZnO layer helped fully bond the interface. Additionally, Zhong et al. performed eutectic bonding of Si and diamond, as shown in Fig. 26(c).<sup>93</sup> Multilayers of Ti/Cu/Ti/Au and Ti/Au were deposited on diamond and Si. Two wafers were pre-bonded at room temperature through the diffusion of Au atoms at the interface. The TEM image of the pre-bonded interface is shown in Fig. 26(d). Subsequently, Cu-Au atoms began interdiffusion during low temperature annealing, eventually forming a firm interface. The TEM image of the final interface is depicted in Fig. 26(e), showing multiple boundaries and interfaces. The TBC of this diamond/Si interface was measured to be 103 MW m<sup>-2</sup> K<sup>-1</sup>, a high TBC among diamondrelated interfaces, while the details of thermal measurement process is lacking in the paper. This TBC value needs to be double checked since the interfacial layer is as thick as 250 nm (cannot be treated as an interface in the thermal model) and composed of mixed nanocrystalline metallic alloy.